## SC1259-0

DATASHEET

Version 1.0 December 2021

## **ACCELEROMETER SIGNAL CONDITIONER**

#### **FEATURES:**

- 24 BITS NO MISSING CODES<sup>1</sup>

- FULL SCALE INPUT CAPACITANCE RANGE C<sub>FS</sub> UP TO ±4pF

- NOMINAL CAPACITANCE RANGE C<sub>0</sub> UP TO 17.75pF

- 0.003% INL

- 18 BITS EFFECTIVE RESOLUTION (C<sub>FS</sub>=4pF, OSR=2048)

10 BITS (C<sub>FS</sub>=4pF, OSR=32)

- PROGRAMMABLE DATA OUTPUT RATESUP TO 7.8KHz<sup>2</sup>

- ON CHIP TEMPERATURE SENSOR ACCURACY: DRIFT:

- ON-CHIP OFFSET & GAIN CALIBRATION

- SPI COMPATIBLE

- 3.0V TO 3.6V

- 180nm SCL CMOS standard logic process

- ESD Protection upto ±3KV HBM

#### **DESCRIPTION:**

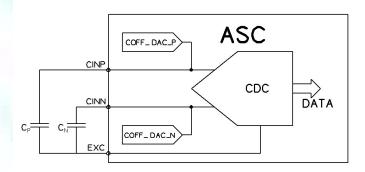

Accelerometer Signal Conditioner (ASC) is a Sigma Delta Modulator based high resolution Capacitance-to-Digital Converter. It senses the change in the differential capacitance connected at the input and produces a 24 Bit digital code proportional to this change. This device is developed for sensing the capacitance change of *MEMS* based Accelerometer and can be used in other similar applications as well. The capacitance to be sensed can be directly connected at the input of this device.

ASC incorporates a Second Order Sigma Delta  $(\Sigma\Delta)$  Modulator. The  $\Sigma\Delta$  Modulator converts the difference in the input differential capacitors into a digital 1 bit pulse train whose average duty cycle represents the digitized signal information. The pulse train is then processed by a digital  $sinc^3$  filter to produce a digital output.

**Notes:** (1) Tested and verified upto 14 Bits. (2) 20MHz Clock Input

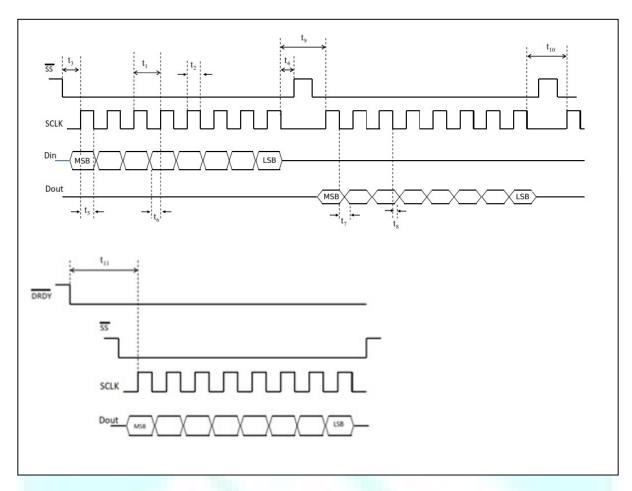

#### **PIN CONFIGURATION:**

#### **PIN DESCRIPTIONS:**

| PIN<br>NO. | NAME | ANALOG/DIGITAL | DESCRIPTION                                                                                                                  |

|------------|------|----------------|------------------------------------------------------------------------------------------------------------------------------|

| 1          | DVDD | Digital Supply | 3.3 V – Digital Supply                                                                                                       |

| 2          | DVSS | Digital Ground | 0 V – Digital Ground                                                                                                         |

| 3          | CINP | Analog Input   | CDC Positive Capacitive Input. The positive side capacitor in differential capacitance to be connected between CINP and EXC. |

| 4          | CINN | Analog Input   | CDC Negative Capacitive Input. The Negative side capacitor in differential capacitance to be connected between CINN and EXC. |

| 5          | EXC  | Analog Output  | CDC Excitation Voltage. This pin should be connected to common terminal of the differential capacitance to be measure.       |

| 6  | VCM      | Analog Output              | Common Mode Output (VDD/2). User has to connect a decoupling capacitor of 0.1µF and 1µF at this pin) |  |  |  |  |  |

|----|----------|----------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7  | TEMP_OUT | Analog Output              | Output of Temperature Sensor                                                                         |  |  |  |  |  |

| 8  | AVDD     | Analog Supply              | 3.3 V – Analog Supply                                                                                |  |  |  |  |  |

| 9  | AVSS     | Analog Ground              | 0 V – Analog Ground                                                                                  |  |  |  |  |  |

| 10 | RESET    | Digital Input: Active Low  | Reset Signal: Reset the entire Chip                                                                  |  |  |  |  |  |

| 11 | CLK      | Digital Input              | Master Clock                                                                                         |  |  |  |  |  |

| 12 | SS_N     | Digital Input: Active Low  | Chip Select                                                                                          |  |  |  |  |  |

| 13 | SCK      | Digital Input              | Serial Clock Input                                                                                   |  |  |  |  |  |

| 14 | DIN      | Digital Input              | Serial Data Input                                                                                    |  |  |  |  |  |

| 15 | DOUT     | Digital Output             | Serial Data Output                                                                                   |  |  |  |  |  |

| 16 | DRDY     | Digital Output: Active Low | Data Ready Signal                                                                                    |  |  |  |  |  |

## **TIMING SPECIFICATIONS:**

#### **TIMING SPECIFICATION TABLES:**

| SPEC            | DESCRIPTION                                                                                             | MIN     | MAX | UNIT                    |

|-----------------|---------------------------------------------------------------------------------------------------------|---------|-----|-------------------------|

| t <sub>1</sub>  | SCLK period                                                                                             | 4 cycle |     | t <sub>CLK</sub> Period |

| t <sub>2</sub>  | SCLK pulse width (High and Low)                                                                         | 2 cycle |     | t <sub>CLK</sub> Period |

| $t_3$           | SS low to first SCLK edge                                                                               | 100     |     | ns                      |

| $t_4$           | Last SCLK falling edge to SS HIGH                                                                       | 100     |     | ns                      |

| t <sub>5</sub>  | SCK rising edge to DIN valid (Hold time)                                                                | 50      |     | ns                      |

| t <sub>6</sub>  | DIN valid to SCLK rising edge (Setup time)                                                              | 50      |     | ns                      |

| t <sub>7</sub>  | SCLK falling Edge to valid new Dout                                                                     |         | 50  | ns                      |

| t <sub>8</sub>  | SCLK falling Edge to DOUT, Hold Time                                                                    | 0       |     | ns <sup>2</sup>         |

| t <sub>9</sub>  | Delay between last SCLK edge of 1st byte                                                                | 50      |     | t <sub>CLK</sub> Period |

|                 | transfer and first SCLK edge for subsequent 2nd<br>byte transfer :<br>RDATA, RDATAC, RREG, WREG Command |         |     |                         |

| t <sub>10</sub> | Final SCLK edge of one command until first edge SCLK of next command                                    | 4       |     | t <sub>CLK</sub> Period |

| t <sub>11</sub> | DRDY LOW to first SCLK edge of first byte transfer for RDATAC command                                   | 15      |     | t <sub>CLK</sub> Period |

| t <sub>11</sub> | DRDY LOW to first SCLK edge of first byte transfer for RDATA command                                    | 0       |     | t <sub>CLK</sub> Period |

Notes: (1) DOUT goes immediately into tri-state whenever SS is high (2) DOUT should be sampled externally on rising edge of SCLK. DOUT will remain valid till next falling edge.

## **ELECTRICAL CHARACTERISTICS**

All Specifications AVDD, DVDD =  $\pm 3.3$ V, Temp. =  $25^{\circ}$ C, OSR = 2048,  $f_{\rm EXC}$  = 250 KHz,  $f_{\rm CLK}$  = 4 MHz,  $f_{\rm DATA}$  = 122 Hz, full scale input capacitance range =  $\pm 4$ pF, unless otherwise specified.

| PARAMETER                                | TESTS CONDITIONS                                          |                           | SC1259-0                |                        | UNITS           |  |

|------------------------------------------|-----------------------------------------------------------|---------------------------|-------------------------|------------------------|-----------------|--|

| CAPACITIVE INPUT                         |                                                           | MIN                       | TYP                     | MAX                    |                 |  |

| Analog Input Range                       |                                                           | 0                         |                         | AVDD                   | V               |  |

| Full Scale Input Range                   | $V_{INP}$ - $V_{INN}$                                     | V <sub>REF</sub> /PG<br>A |                         | +V <sub>REF</sub> /PGA | V               |  |

| Programmable Gain Amplifier              | User Selectable                                           | 1                         |                         | 128                    |                 |  |

| Static Input Current                     |                                                           |                           |                         | 1.0                    | μA              |  |

| Input Capacitance                        |                                                           |                           | 32                      |                        | pF              |  |

| Bandwidth<br>Sinc <sup>3</sup> Filter*** | -3dB                                                      |                           | 0.262*f                 |                        | Hz              |  |

|                                          | Modulator                                                 |                           | 0.262*f <sub>Data</sub> |                        |                 |  |

| Differential Input Impedance             | Frequency=78KHz                                           |                           | 100                     |                        | ΚΩ              |  |

| DEVICE PERFORMANCE                       |                                                           |                           |                         |                        |                 |  |

| Resolution                               | 00D 540 f 5MH- f                                          | 24                        |                         |                        | Bits            |  |

| No Missing Code*                         | $OSR=512, f_{CLK} = 5MHz, f_{MOD}$ $= f_{CLK}/32$         | 14                        |                         |                        | Bits            |  |

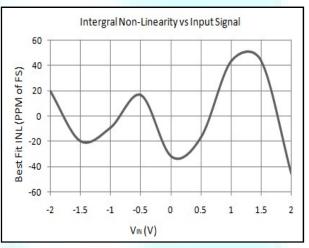

| Integral Non-Linearity                   | Best Fit Method                                           |                           |                         | ±0.003                 | % of FS         |  |

| mogram ton Embanty                       | Boot i it illouieu                                        |                           |                         | _0.000                 | 70 01 1 0       |  |

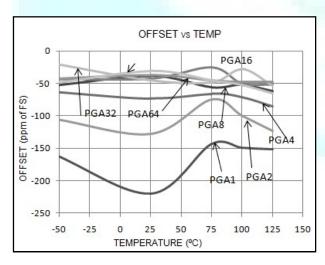

| Offset Error**                           | Before Calibration                                        |                           |                         | 220                    | ppm of          |  |

| Oligat Ellar                             | Belefe Gallstation                                        |                           |                         | 220                    | FS              |  |

| Offset Drift                             | -40°C to +125°C                                           |                           |                         | 0.22                   | ppm of<br>FS/°C |  |

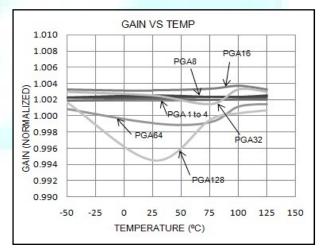

| Gain Error                               | Before Calibration                                        |                           |                         | 0.225                  | % of FS         |  |

| Gain Drift                               | -40°C to +125°C                                           |                           |                         | 0.303                  | ppm /°C         |  |

|                                          |                                                           |                           |                         |                        |                 |  |

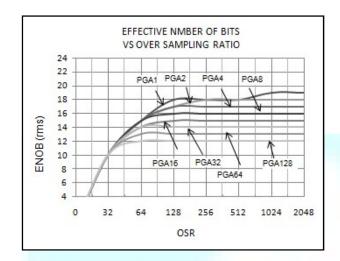

| Effective Number of Bits                 | Based on 100 samples                                      |                           |                         | 19                     | Bits            |  |

| (ENOB)                                   |                                                           |                           |                         |                        |                 |  |

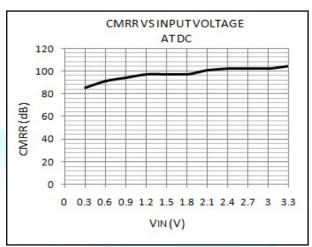

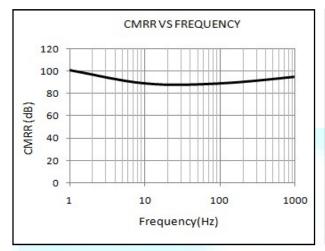

| Common-Mode Rejection                    | At DC                                                     |                           | 102                     |                        | dB              |  |

|                                          | $f_{\text{CM}}$ =10Hz, $f_{\text{DATA}}$ =30Hz            |                           | 89                      |                        | dB              |  |

|                                          | $f_{\text{CM}}=100\text{Hz}, f_{\text{DATA}}=30\text{Hz}$ |                           | 89                      |                        | dB              |  |

|                                          | $f_{CM}$ =1KHz, $f_{DATA}$ =30Hz                          |                           | 95                      |                        | dB              |  |

|                                          |                                                           |                           |                         |                        |                 |  |

| ON CHIP TEMP SENSOR                      |                                                           |                           |                         |                        |                 |  |

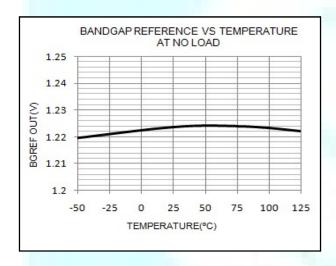

| Output Voltage                           | No Load                                                   | 1.220                     | 1.2223                  | 1.230                  | V               |  |

| Drift                                    |                                                           |                           |                         | ±20                    | ppm/°C          |  |

| Start up Time***<br>Load Regulation      | @Full Load Current = 2.5mA                                |                           |                         | 50<br>1.0              | μS<br>%         |  |

| EXCITATION                               | Gran Eoad Garrent - 2.5mA                                 |                           |                         | 1.0                    | 70              |  |

| VREF                                     | (REFIN+)-(REFIN-)                                         |                           |                         | 2.5                    | V               |  |

| CLOCK INPUT**** fclk                     |                                                           |                           | 5                       | 20                     | MHz             |  |

| POWER SUPPLY                             |                                                           |                           |                         |                        |                 |  |

| REQUIREMENT                              | AVDD AVDDO                                                |                           |                         |                        |                 |  |

| Supply Voltage                           | AVDD, AVDDO,<br>DVDDO,MVDD                                | 3.0                       | 3.3                     | 3.6                    | V               |  |

|                                          | DVDD                                                      | 1.62                      | 1.8                     | 1.98                   | V               |  |

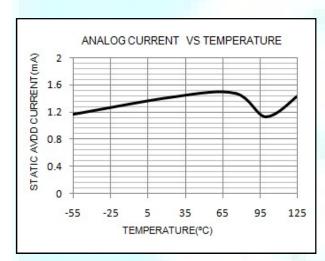

| Analog Current                           |                                                           |                           | 1.6                     | 2.5                    | mA              |  |

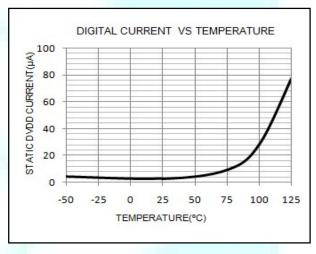

| Digital Current                          |                                                           |                           |                         | 600                    | μΑ              |  |

| TEMPERATURE RANGE                        |                                                           |                           |                         |                        |                 |  |

| Operating                                | <u> </u>                                                  | -55                       | <u> </u>                | 125                    | °C              |  |

<sup>\*</sup>Missing codes are verified and tested upto 14bits. Device may perform for better results. \*\*Calibration can minimize this error. \*\*\*Simulated Result

### **ELECTRICAL CHARACTERISTICS**

All Specifications AVDD, DVDD =  $\pm 3.3$ V, Temp. =  $25^{\circ}$ C, OSR = 2048,  $f_{EXC}$  = 250 KHz,  $f_{CLK}$  = 4 MHz,  $f_{DATA}$  = 122 Hz, full scale input capacitance range =  $\pm 4$ pF, unless otherwise specified.

### **ELECTRICAL CHARACTERISTICS**

All Specifications AVDD, DVDD =  $\pm 3.3$ V, Temp. =  $25^{\circ}$ C, OSR = 2048,  $f_{EXC}$  = 250 KHz,  $f_{CLK}$  = 4 MHz,  $f_{DATA}$  = 122 Hz, full scale input capacitance range =  $\pm 4$ pF, unless otherwise specified.

#### **DIGITAL CHARACTERISTICS**

DVDDO= 3.0V to 3.6V

| PARAMETER                     | TESTS CONDITIONS                             |      | UNITS |      |       |

|-------------------------------|----------------------------------------------|------|-------|------|-------|

| PARAMETER                     | TESTS CONDITIONS                             | MIN  | TYP   | MAX  | UNITS |

| Logic Family                  |                                              |      | CMOS  |      |       |

| Logic Level: V <sub>IH</sub>  |                                              | 2    |       | DVDD | V     |

| V <sub>IL</sub>               |                                              | DVSS |       | 0.8  | V     |

| V <sub>OH</sub>               | I <sub>OH</sub> =8mA<br>I <sub>OL</sub> =8mA | 3.0  |       |      | V     |

| $V_{OL}$                      | I <sub>OL</sub> =8mA                         | DVSS |       | 0.4  | V     |

| Input Leakage: I <sub>⊪</sub> | V <sub>I</sub> =DVDD                         |      |       | 1    | μA    |

| I <sub>IL</sub>               | V <sub>I</sub> =DVSS                         | -1   |       |      | μA    |

## **ABSOLUTE MAXIMUM RATING**

| PARAMETER                      | SC1259-0 |          |       |  |  |

|--------------------------------|----------|----------|-------|--|--|

| PARAMETER                      | MIN      | MAX      | UNITS |  |  |

| AVDD to AVSS                   | -0.3     | 4.3      | V     |  |  |

| DVDD to DVSS                   | -0.3     | 4.3      | V     |  |  |

| DVDD18 to DVSS                 | -0.3     | 2.2      | V     |  |  |

| INP, INN                       | -0.3     | AVDD+0.3 | V     |  |  |

| Digital Input Voltage to DGND  | -0.3     | DVDD+0.3 | V     |  |  |

| Digital Output Voltage to DVSS | -0.3     | DVDD+0.3 | V     |  |  |

| Digital Output Current         |          | 8        | mA    |  |  |

| Maximum Ambient Temperature    |          | 125      | °C    |  |  |

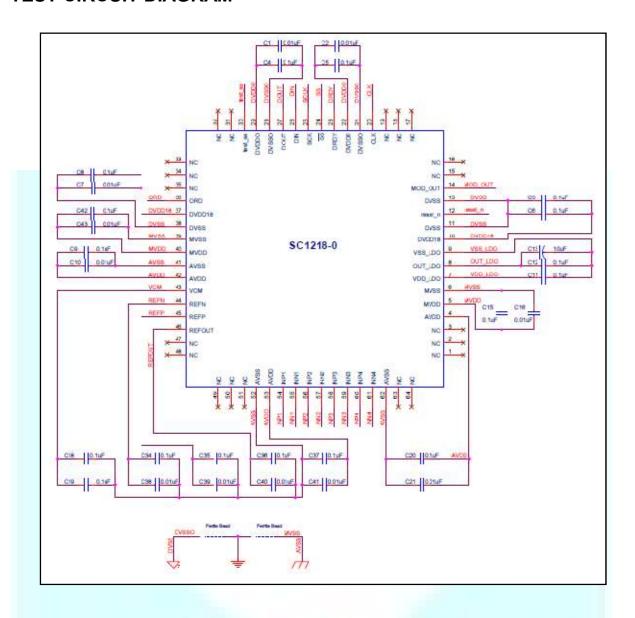

#### **TEST CIRCUIT DIAGRAM**

#### PCB LAYOUT RECOMMENDATION

The test / application board should be four layer PCB. To achieve high performance surface mount components to be used wherever possible. This reduces the trace length and minimizes the effects of parasitic capacitance and inductance. The board should use separate ground with all the analog signals and the digital signals. Bypass capacitors are strongly recommended at power supply and reference pins of the converter. User should also use R-C filter (49.9 $\Omega$  and 47pF) on each input to have better performance.

#### **OVERVIEW**

#### SIGMA DELTA MODULATOR

A second order single loop modulator is used in the ASC. The  $\Sigma\Delta$ Modulator converts the change in the input differential capacitance into a digital pulse train whose average duty cycle represents the digitized signal information. As mentioned above the, the full scale input capacitance range ASC is programmable.  $C_{FS}$ C<sub>DiffMax</sub> of any Depending on the sensor, user can set any value of  $C_{ES}$ between 0.5pF and 4pF in steps of 0.5pF. The  $C_{FS}$  must be selected in such a way so that C<sub>DiffMax</sub> should not be more than  $C_{FS}$  under full scale input **CFS** The conditions. can be programmed using CF2: CF0 bits of control register CR1 as given in the following table:

| FS2:FS1:FS0 | C <sub>FS</sub> (pF) |

|-------------|----------------------|

| 000         | ±4                   |

| 001         | ±3.5                 |

| 010         | ±3                   |

| 011         | ±2.5                 |

| 100         | ±2                   |

| 101         | ±1.5                 |

| 110         | ±1                   |

| 111         | ±0.5                 |

The values mentioned in the Table 5 are the typical values of  $C_{FS}$ . There may be 20% change in these values. The modulator runs at clock frequency  $f_{MOD}$ , which is same as the excitation source frequency  $f_{EXC}$ .  $f_{EXC}$  and  $f_{MOD}$  can be adjusted by setting the appropriate value of PRE1: PRE0 of CR2 control register as shown in the following table:

| PRE1:PRE0 | $f_{EXC}$ and $f_{MOD}$ |

|-----------|-------------------------|

| 00        | f <sub>CLK</sub> /16    |

| 01        | f <sub>CLK</sub> /32    |

| 10        | f <sub>CLK</sub> /64    |

| 11        | f <sub>CLK</sub> /128   |

Where,  $f_{CLK}$  is external clock frequency. The modulator is designed to work at a maximum sampling frequency of 250 KHz.

#### PROGRAMMABLE DIGITAL FILTER

The  $\sum \Delta$  Modulators is followed by an integrated digital filter unit. It comprises of  $sinc^3$  digital filter and internal registers. The Decimation Ratio or Oversampling Ratio (OSR) of filter module can be programmed. The on-chip digital filter processes the single bit data stream coming from the corresponding modulator unit using a  $sinc^3$  filter. The output Data Rate (DR) of digital filter is given as:

### Data Rate = $f_{MOD}$ / OSR

The 3dB cut off frequency of the filter is 0.262 \* DR. For example, if  $f_{MOD}$  is 250 KHz and OSR is 256, then the Data Rate comes out to be 976Hz and maximum input frequency will be 0.262\*244 i.e. 255Hz.

The *OSR* of filter can vary from 20 to 2047 and its value is represented by 8 Bits of *DECIM* Register and first 3 LSBs of *CR2* Register. Although, *OSR* can have any of the value between 20 and 2047 but there are fixed numbers of OSRs which are implemented internally. A range of the OSR belongs to a particular fixed internal OSR. Depending on the selected OSR value from a particular range, filter will provide a gain. The gain of the filter will be:

$$FilterGain = \left(\frac{OSR}{Internal\ OSR}\right)^{3}$$

A table is given below shows the Filter Gain on a various decimation ratio:

**Table 7: Oversampling Ratio**

| S.<br>No. | Internal<br>OSR | OSR I | Range | Filter Gain |      |  |  |

|-----------|-----------------|-------|-------|-------------|------|--|--|

|           |                 | MAX   | MIN   | MAX         | MIN  |  |  |

| 1         | 2048            | 2047  | 1836  | 0.99        | 0.72 |  |  |

| 2         | 1626            | 1835  | 1458  | 1.44        | 0.72 |  |  |

| 3         | 1260            | 1457  | 1157  | 1.44        | 0.72 |  |  |

| 4         | 1024            | 1156  | 919   | 1.44        | 0.72 |  |  |

| 5         | 813             | 918   | 729   | 1.44        | 0.72 |  |  |

| 7         | 645             | 728   | 579   | 1.44        | 0.72 |  |  |

| 8         | 512             | 578   | 459   | 1.44        | 0.72 |  |  |

| 9         | 406             | 458   | 365   | 1.43        | 0.72 |  |  |

| 10        | 323             | 364   | 290   | 1.43        | 0.72 |  |  |

| 11        | 256             | 289   | 230   | 1.44        | 0.72 |  |  |

| 12        | 203             | 229   | 182   | 1.43        | 0.72 |  |  |

| 13        | 161             | 181   | 145   | 1.41        | 0.73 |  |  |

| 14        | 128             | 144   | 115   | 1.42        | 0.72 |  |  |

| 15        | 102             | 114   | 92    | 1.41        | 0.74 |  |  |

| 16        | 81              | 91    | 73    | 1.44        | 0.74 |  |  |

| 17        | 64              | 72    | 58    | 1.42        | 0.74 |  |  |

| 18        | 51              | 57    | 46    | 1.41        | 0.74 |  |  |

| 19        | 40              | 45    | 36    | 1.39        | 0.71 |  |  |

| 20        | 32              | 35    | 29    | 1.31        | 0.74 |  |  |

| 21        | 25              | 28    | 23    | 1.34        | 0.74 |  |  |

| 22        | 20              | 20    | 22    | 1.3         | 1    |  |  |

Depending on the value on OSR, user can calculate Filter Gain. The output code of the filter data will be scaled by the corresponding Filter Gain. For e.g., If OSR = 1350, the Corresponding Internal OSR of the filter is 1260 (S. No. 3), then the filter gain is given as:

$$FilterGain = \left(\frac{1350}{1260}\right)^3 = 1.23$$

The filter gain can be corrected using Gain Calibration.

The  $\Sigma\Delta$  modulator along with the programmable digital filter forms the Capacitance-to-Digital (CDC) Converter.

#### **EXCITATION SOURCE**

It provides excitation to the differential input capacitance. The capacitance to be measured should be connected between EXC and ASC input (CINP and CINN) as shown in Fig xx. ASC outputs a square wave on ECX pin.

The amplitude  $V_{EXC}$  and frequency  $f_{EXC}$ square wave programmable. The voltage appears across the input capacitors  $C_P$  and  $C_N$ will be half of  $V_{EXC}$ . For e.g. if  $V_{EXC}$  is VDD, then ±VDD/2 will appear across the input capacitors  $C_P$  and  $C_N$ .  $f_{FXC}$ programmed can be PRE1:PRE0 bits of CR2 control register as mentioned in Table 5.  $V_{EXC}$ be programmed EXC1:EXC0 control bits of control register CR1.

| EXC1:EXC0 | V <sub>EXC</sub> |  |  |  |

|-----------|------------------|--|--|--|

| 00        | VDD              |  |  |  |

| 01        | ±3VDD/4          |  |  |  |

| 10        | ±VDD/2           |  |  |  |

| 11        | ±VDD/4           |  |  |  |

The common mode voltage of  $V_{EXC}$  is VDD/2.

#### **CAPDAC**

The input capacitance full scale range  $C_{FS}$  of the ASC is programmable. Depending on full scale capacitance of the Sensor, user can program the value of CFS from 0.5pF to 4pF in steps of 0.5pF.

ASC can accept higher nominal capacitance  $C_0$  of differential sensor. The nominal capacitance of the sensor

can be balanced using CAPDAC. CAPDAC is the negative capacitance connected at the input pin. As shown in Fig. 6, ASC consists of two independent CAPDACs; CAPDAC P to balance the capacitance on CINP and CAPDAC N to balance the capacitance on CINN. The effective capacitance of CINP CINPeff will be the difference of C<sub>P</sub> and CAPDAC P. Similarly effective capacitance of *CINN*  $C_{INNeff}$  will be the difference of  $C_N$  and CAPDAC N. The differential capacitance which will be sensed by the ASC is given as:

$$C_{Diff} = C_{INPeff} - C_{INNeff}$$

=  $(C_P - CAPDAC_P) - (C_N - CAPDAC_N)$

The maximum possible value of CAPDAC P and CAPDAC N is 15.75pF and its resolution is 0.25pF. The values of CAPDAC P CAPDAC N can be set independently using the CAPDAC\_P5:CAPDAC\_P0 control bits of CAPDAC\_P register and CAPDAC\_N5:CAPDAC\_N0 control bits of CAPDAC N register respectively. Typically, the total value

of each CAPDAC (CAPDAC\_P and CAPDAC\_N) is given as:

C<sub>CAPDAC\_P</sub> = 0.25 pF\*(Decimal Equivalent of CAPDAC\_P5:CAPDAC\_P0) For e.g. if decimal equivalent of  $CAPDAC\_P5:CAPDAC\_P0$  is 17, then  $C_{CAPDAC\_P}$  will be 4.25pF. If decimal equivalent of  $CAPDAC\_N5:CAPDAC\_N0$  is 63, then  $C_{CAPDAC\_N}$  will be 15.75pF.

The *CAPDACs* should be used if value of  $C_P$  or  $C_N$  is more than  $C_{FS}$ . When  $C_P$  or  $C_N$  is more than  $C_{FS}$ , then user should set the *CAPDAC\_P* and *CAPDAC\_P* in such a way so that under full scale input conditions,  $C_{INPeff}$  and  $C_{INNeff}$  should not be more than  $C_{FS}$ .

Few cases of selecting appropriate value of  $C_{FS}$  and both the CAPDACs as well as the corresponding ideal digital code (assuming 2's Compliment Data Format) are tabulated in Table 9.

As, it can be seen from above table that in any case,  $C_{INPeff}$  and  $C_{INNeff}$  is not more than  $C_{FS}$ . For the same value of  $C_0$  and  $C_{FS}$ , user can used different combinations of COFFDAC as shown in Case2 and 3. It is recommended that USER should not use COFFDAC unless it is not required.

C<sub>CAPDAC\_N</sub> = 0.25 pF\*(Decimal Equivalent of CAPDAC N5:CAPDAC N0)

| S.  | Innut | C <sub>0</sub> | C <sub>Diffmax</sub> | $C_P$ | $C_N$ | $C_{FS}$ | CAPDAC_P | CAPDAC_N | C <sub>INPeff</sub> | C <sub>INNeff</sub> | $C_{Diff}$ | Ideal   |

|-----|-------|----------------|----------------------|-------|-------|----------|----------|----------|---------------------|---------------------|------------|---------|

| No. | Input | (pF)           | (pF)                 | (pF)  | (pF)  | (pF)     | (pF)     | (pF)     | (pF)                | (pF)                | (pF)       | Digital |

|     |          |       |   |       |       |   |       |       |      |      |    | Code   |

|-----|----------|-------|---|-------|-------|---|-------|-------|------|------|----|--------|

|     | 0        | 2     | 4 | 2     | 2     | 4 | 0     | 0     | 2    | 2    | 0  | 000000 |

| 1   | +ve F.S. | 2     | 4 | 4     | 0     | 4 | 0     | 0     | 4    | 0    | 4  | 7FFFFF |

|     | -ve F.S. | 2     | 4 | 0     | 4     | 4 | 0     | 0     | 0    | 4    | -4 | 800000 |

|     | 0        | 6     | 2 | 6     | 6     | 2 | 5     | 5     | 1    | 1    | 0  | 000000 |

| 2.1 | +ve F.S. | 6     | 2 | 7     | 5     | 2 | 5     | 5     | 2    | 0    | 2  | 7FFFFF |

|     | -ve F.S. | 6     | 2 | 5     | 7     | 2 | 5     | 5     | 0    | 2    | -2 | 800000 |

|     | 0        | 6     | 2 | 6     | 6     | 2 | 7     | 5     | -1   | -1   | 0  | 000000 |

| 2.2 | +ve F.S. | 6     | 2 | 7     | 5     | 2 | 7     | 5     | 0    | -2   | 2  | 7FFFFF |

|     | -ve F.S. | 6     | 2 | 5     | 7     | 2 | 7     | 5     | -2   | 0    | -2 | 800000 |

|     | 0        | 10    | 3 | 10    | 10    | 3 | 8.5   | 8.5   | 1.5  | 1.5  | 0  | 000000 |

| 3.1 | +ve F.S. | 10    | 3 | 11.5  | 8.5   | 3 | 8.5   | 8.5   | 3    | 0    | 3  | 7FFFFF |

|     | -ve F.S. | 10    | 3 | 8.5   | 11.5  | 3 | 8.5   | 8.5   | 0    | -3   | -3 | 800000 |

|     | 0        | 10    | 3 | 10    | 10    | 3 | 11.5  | 11.5  | -1.5 | -1.5 | 0  | 000000 |

| 3.2 | +ve F.S. | 10    | 3 | 11.5  | 8.5   | 3 | 11.5  | 11.5  | 0    | -3   | 3  | 7FFFFF |

|     | -ve F.S. | 10    | 3 | 8.5   | 11.5  | 3 | 11.5  | 11.5  | -3   | 0    | -3 | 800000 |

|     | 0        | 17.75 | 4 | 17.75 | 17.75 | 4 | 15.75 | 15.75 | 2    | 2    | 0  | 000000 |

| 4   | +ve F.S. | 17.75 | 4 | 19.75 | 15.75 | 4 | 15.75 | 15.75 | 4    | 0    | 4  | 7FFFFF |

|     | -ve F.S. | 17.75 | 4 | 15.75 | 19.75 | 4 | 15.75 | 15.75 | 0    | -4   | -4 | 800000 |

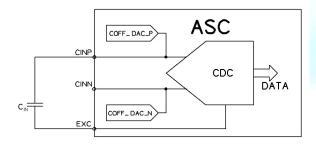

### Single Ended Capacitance Measurement Mode of ASC

ASC is developed for the differential mode capacitance measurements. But the device can also be used for Single Ended Capacitance Measurement as well. The Single Ended Sensor  $C_{IN}$  can be connected between EXC and CINP and CINN can be left open as shown in Fig. 7.

As explained in the  $\sum \Delta$  Modulator section previously, USER should select  $C_{FS}$  range depending on the maximum capacitance change ( $C_{inFS}$ ) possible in sensor capacitance. The  $C_{FS}$  should be selected in such a way so that  $C_{inFS}$  must always be less than

or equal to  $C_{FS}$ .

The nominal capacitance  $C_0$  (Not Changing) of input sensor must be balanced using CAPDAC. ASC will

produce the digital code corresponding to the capacitance  $C_{Single}$ .

$$C_{Single} = (C_{IN} - (CAPDAC_P - CAPDAC_N))$$

The value of both the CAPDACs must be set equal to nominal value  $C_0$  of input sensor. Because of limited resolution of CAPDAC, if it is not possible to set CAPDACs equal C0, then it must be set nearest to C0 and the initial difference between CAPDAC and C0 can be taken care of System Offset Calibration, if the difference is within the calibration range. In single ended case, ASC can handle the Nominal capacitance up to 15.75pF.

In case of Single Ended case, if the 2's compliment data format is selected, then output code will vary from 000000 to 7FFFFF and if unipolar data format mode is selected then output code will vary from 000000 to FFFFFF. Assuming Unipolar Data Format is selected, a table is given below for selection of CFS and CAPDACs:

| S.  | Innut | C₀   | CinFS | C <sub>IN</sub> | $C_{FS}$ | CAPDAC_P | CAPDAC_N | C <sub>Single</sub> | Ideal   |

|-----|-------|------|-------|-----------------|----------|----------|----------|---------------------|---------|

| No. | Input | (pF) | (pF)  | (pF)            | (pF)     | (pF)     | (pF)     | (pF)                | Digital |

|   |          |       |   |       |   |       |    |   | Code   |

|---|----------|-------|---|-------|---|-------|----|---|--------|

| 1 | 0        | 0     | 4 | 0     | 4 | 0     | 0  | 0 | 000000 |

| ' | +ve F.S. | 0     | 4 | 4     | 4 | 0     | 0  | 4 | FFFFFF |

| 2 | 0        | 4     | 2 | 4     | 2 | 4     | 4  | 0 | 000000 |

|   | +ve F.S. | 4     | 2 | 6     | 2 | 4     | 4  | 2 | FFFFFF |

| 2 | 0        | 10    | 1 | 10    | 1 | 10    | 10 | 0 | 000000 |

| 3 | +ve F.S. | 10    | 1 | 11    | 1 | 10    | 10 | 1 | FFFFFF |

| 4 | 0        | 15.75 | 4 | 15.75 | 4 | 15.75 | 4  | 0 | 000000 |

| 4 | +ve F.S. | 15.75 | 4 | 19.75 | 4 | 15.75 | 4  | 4 | FFFFFF |

#### **SERIAL INTERFACE**

The serial interface is standard fourwire SPI compatible (DIN, DOUT, SCK and SS\_N). USER can communicate to ASC using serial interface. The SPI works in mode 00 i.e. clock phase is 0 and clock polarity is also 0. SPI serial interface signals are described below:

## SS\_N (Serial Interface Enable)

The SS\_N input must be externally asserted before a master device can exchange data with the ADC. SS\_N must be low for the duration of the transaction. DOUT pin will become tristate when SS\_N goes high. After data read operation, it should be made high.

#### SCK (serial clock)

SCK function as a clock for serial communication. The device will sample serial data on positive edge of SCK. Data from PSSC will be launched on negative edge of SCK.

#### **DIN (Data input)**

DIN is the serial data input port. DIN is internally sampled at positive edge of SCK by SPI.

#### **DOUT (Data Output)**

DOUT is the serial data output port. DOUT is internally launched by SPI at negative edge of SCK by SPI. DOUT immediately goes into tri-state when

SS\_N is high.

### **DRDY (DATA READY)**

The DRDY pin is used as a status signal to indicate when new digital code is ready to be read from the ASC. DRDY goes low when new data is available. It goes high in the mid of the byte read second during operation from the data register. In case, in response to the DRDY assertion read operation no performed, DRDY will remain low till next Data cycle. It is mandatory for the user to read at least two bytes, otherwise the DRDY will remains low till next Data cycle.

#### **CALIBRATION**

The offset and gain errors in the ASC or the complete system, can be reduced with calibration. User can carry out system calibration to reduce offset and gain errors. For system calibration, the appropriate capacitor must be connected to the inputs. The system offset calibration command requires a "zero" differential capacitor CDiff. It then computes an offset that will nullify offset in the system. The system gain calibration command requires a positive full scale CDiff i.e. CDiff = CFS. It then computes a value to nullify gain errors in the system. At completion of calibration, the DRDY signal will go LOW to indicate that calibration is complete and valid data is available. (Note: To read internal Offset Correction Register

(OCR) and Full Scale Register (FSR) value, RREG command should be used with appropriate register address.)

SYSTEMOCAL commands will only update the Offset Calibration Register of the ASC with appropriate offset value. However, to enable the offset correction, OCEN bit of CR1 control register has to be set separately. Similarly to enable the Gain Calibration set GCALEN bit of CR1. The offset gain calibration module can correct up to 50% of Full Scale Range. Calibration of ASC must be performed after system reset, a change in decimation ratio, a change in CFS, a change in the COFFDEC value, or a change in Excitation source frequency or Amplitude.

Apart from above commands, OSR and FSR of the selected ADC core can be accessed externally through RREG (Read Register) and WREG (Write Register) commands. This will provide flexibility to manually set the OCR and FSR. When FSR is externally loaded, follow the procedure as below:

- Perform System gain calibration as sated above and read the FSR register and note down the value.

- Divide FFFFC00000 by noted value of FSR register and take its integer portion.

- This calculated value has to be written into FSR register at next power ON in order to perform gain calibration without command.

#### For example:

Let us assume noted value of FSR register is 3ee259.

The value to be written in the FSR reg. after power off and on will be: FFFFC00000/3ee259 = 4122B7.

#### **OVER-LOAD & OVER-RANGE**

#### **DETECTION MODULE:**

These Modules prevents rollover of digital output code when differential capacitance of sensor  $C_{Diff}$  exceeds the full scale capacitance range  $C_{FS}$ . Digital output code will be clipped at  $(7FFFFF)_H$  and  $(800000)_H$  when  $C_{Diff}$  exceeds positive and negative full scale respectively. In case the ADC input is more than 50 % of full scale range, the Over Load detection module will clipped the digital output at  $(7FFFFF)_H$  or  $(8000000)_H$  accordingly.

Over-Range Detection Module also keeps into consideration of digital calibration. i.e. Any rollover of digital output due to calibration will also be detected by Over Range Detection Module and will be clipped appropriately (7FFFFF)<sub>H</sub> and to  $(800000)_{H}$  . To ensure the proper functioning of the Over Detection Module, following constraint on OCR & FSR register value must be followed:

- Maximum value of OCR register should not exceed 3FFFF<sub>H</sub> for negative offset correction and C00000<sub>H</sub> for positive offset correction.

- 2. FSR value must be positive.

By default Over-Load and Over-Range Detection Modules are enabled.

- Over-Load Detection module (OLDD)

- > In the scenario where digital code without calibration is such that it cannot be corrected after calibration Over-Load then detection module detects overload and clip digital output appropriately to (7FFFF)<sub>H</sub> and  $(800000)_{H}$

- Over-load detection can be disabled by setting OLDD bit of CR2 control register.

- 2. Over-Range Detection module (ORDD)

- ➢ Over-range module checks for the digital code after digital offset and gain calibration. If digital code after gain and offset calibration is out of the acceptable code range then digital over-range module detects over-range and clip digital output appropriately to (7FFFFF)<sub>H</sub> and (800000)<sub>H</sub>.

- Over-range detection can be disabled by setting ORDD bit of CR2 control register.

Over-Load Detection and Over-Range Detection can be disabled by setting OLDD and ORDD bits of CR2 register respectively. ORDD bit also affects digital output range. Setting ORDD bit will half the digital output range as shown in Table-7. In case of Over-Load or Over-Range detection, the primary output pin ORD will become high. This ORD pin will be correspond to the selected ADC core.

Table 11: Full scale code range correspond to different DOVDD flag value

| ORDD bit | $C_{Diff}$       | DIGITAL OUTPUT<br>CODE |  |  |

|----------|------------------|------------------------|--|--|

|          | +C <sub>FS</sub> | 7FFFFF <sub>H</sub>    |  |  |

| ORDD = 0 | 0                | 000000 <sub>н</sub>    |  |  |

|          | -C <sub>FS</sub> | 800000 <sub>H</sub>    |  |  |

|          | +C <sub>FS</sub> | 3FFFFF <sub>H</sub>    |  |  |

| ORDD = 1 | 0                | 000000 <sub>н</sub>    |  |  |

|          | -C <sub>FS</sub> | С00000 <sub>н</sub>    |  |  |

**Table 12: Output Data Format**

| C <sub>Diff</sub> | Unipolar | Two's      |  |  |

|-------------------|----------|------------|--|--|

|                   |          | Compliment |  |  |

| -C <sub>FS</sub>  | 000000   | 800000     |  |  |

| 0                 | 000000   | 000000     |  |  |

| +C <sub>FS</sub>  | FFFFFF   | 7FFFFF     |  |  |

## **TEMPERATURE SENSOR**

An on chip temperature sensor is provided whose output is independently available in analog form. In case user wants to digitize the output of the temperature sensor, its output should be shorted externally with the input of one of the ADC. The temperature sensor is PTAT based temperature sensor.

#### **OUTPUT CODE FORMAT**

Two options of the output data format are available in SC1259: Two's Compliment and Unipolar. Any of the data format may be chosen based on the Data format bit CR2.

## **COMMAND DEFINITIONS**

The commands listed below control the operation of SC1259-0 Device. Some commands are stand-alone commands (e.g. STOPC) while others require additional bytes (e.g., WREG requires command and the data bytes).

Operands:

rrrr represents the register address.

nnnnnnn represents the data.

xxxx: these bits will be ignored while instruction decoding.

| COMMANDS | DESCRIPTION                 | COMMAND BYTE                    | 2ND COMMAND BYTE                 |

|----------|-----------------------------|---------------------------------|----------------------------------|

| RDATA    | Read Data                   | 0001 xxxx (1x <sub>H</sub> )    | -N.A                             |

| RDATAC   | Read Data Continuously      | 0011 xxxx (3x <sub>H</sub> )    | -N.A                             |

| STOPC    | Stop Read Data Continuously | 1111 xxxx (Fx <sub>H</sub> )    | -N.A                             |

| RREG     | Read from Register rrrr     | 0100 r r r r (4r <sub>H</sub> ) | -N.A                             |

| WREG     | Write to Register rrrr      | 0101 r r r r (5r <sub>H</sub> ) | nnnn_nnnn<br>(value of reg–rrrr) |

| SYSOCAL  | System Offset Calibration   | 0111 xxxx (7x <sub>H</sub> )    | -N.A                             |

| SYSGAIN  | System Gain Calibration     | 1001 xxxx (9x <sub>H</sub> )    | -N.A                             |

### RDATA (Read Data):

This command reads a single 24-bit ADC conversion result. In response to RDATA command ADC transmit 24-bit digital code. Digital code is available at DOUT pin in 8-bit format with most significant byte first. RDATA command must be followed by 3-byte read operation. On completion of read operation, DRDY goes high.

Operands: None

Bytes: 1

Encoding: 0001 xxxx

digital code. DRDY will go high in response to 3-byte read operation. This mode will be terminated by the STOPC (Stop Read data Continuous) command.

RDATAC command must be followed by STOPC command before issuing any other command.

Operands: None

Bytes: 1

Encoding: 0011 xxxx

## RDATAC (Read Data Continuous)

RDATAC (Read Data Continuous) command enables the continuous output of new data on each DRDY. This command eliminates the need to send the Read Data Command on each DRDY. In case of read data continuous command user can directly perform 3 read operation to read 24-bit

# STOPC (Stop Read Data Continuous)

Description: Ends the continuous data output mode. After this command DRDY will also go high.

Operands: None

Bytes: 1

Encoding: 1111 xxxx

Data Transfer Sequence:

#### RREG (Read Register)

RREG (Read Register) command reads content of the specified register. The address of the register to be read is specified in the LSB nibble of the instruction.

Operands: None

Bytes: 2

Encoding: 0100 rrrr

rrrr: Defines register address as mentioned in the Table 8.

## **WREG** (Write Register)

WREG (Write Register) command writes the data to specified register. The address of the register to be written is specified in the LSB nibble of the instruction. Second byte represents the data to be written.

Operands: r, n

Bytes: 2

Encoding: 0101 rrrr nnnn nnnn

rrrr: Defines register address as

mentioned in the Table 8. nnnn nnnn : value of reg-rrrr

# SYSOCAL (System Offset Calibration):

SYSTEMOCAL command performs system offset calibration. In case of system offset calibration ADC computes the offset value based on the available differential input signal on selected analog channel to nullify offset in the system.

At the end of the calibration process, offset value will be stored in 24-bit internal Offset Calibration Register (OCR). The offset value stored in Offset Calibration Register (OCR) is in

### **CONTROL / STATUS REGISTERS**

2's complement format.

DRDY will be asserted to indicate completion of the command.

Operands: none

Bytes: 1

Encoding: 0111 xxxx

# SYSGAIN (System Gain Calibration):

This command performs System gain Calibration. In case of system offset calibration, the value of the gain calibration coefficient is calculated based on the available input differential signal. At the end of the calibration process, gain calibration coefficient value will be stored in 24-bit internal FSR.

DRDY will be asserted to indicate completion of the command.

Operands: none

Bytes: 1

Encoding: 1001 xxx

The operation of the device is set up through following control / status registers.

| Address        | Register               | BIT7            | BIT6  | BIT5      | BIT4      | віт3      | BIT2      | BIT1      | BIT0      |

|----------------|------------------------|-----------------|-------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0 <sub>н</sub> | digital_code_B1<br>(R) | DC23            | DC22  | DC21      | DC20      | DC19      | DC18      | DC17      | DC16      |

| 1 <sub>H</sub> | digital_code_B2<br>(R) | DC15            | DC14  | DC13      | DC12      | DC11      | DC10      | DC9       | DC8       |

| 2 <sub>H</sub> | digital_code_B3<br>(R) | DC7             | DC6   | DC5       | DC4       | DC3       | DC2       | DC1       | DC0       |

| 3 <sub>H</sub> | CR1 (RW)               | FS2             | FS1   | FS0       | OCEN      | GCALEN    |           | EXC1      | EXC0      |

| 4 <sub>H</sub> | CR2(RW)                | Data_<br>format | OLDD  | ORDD      | PRE1      | PRE0      | OSR10     | OSR9      | OSR8      |

| 7 <sub>H</sub> | DECIM_reg              | OSR7            | OSR6  | OSR5      | OSR4      | OSR3      | OSR2      | OSR1      | OSR0      |

| 8H             | OCR1 (RW)              | OCR7            | OCR6  | OCR5      | OCR4      | OCR3      | OCR2      | OCR1      | OCR0      |

| 9 <sub>H</sub> | OCR2 (RW)              | OCR15           | OCR14 | OCR13     | OCR12     | OCR11     | OCR10     | OCR9      | OCR8      |

| A <sub>H</sub> | OCR3 (RW)              | OCR23           | OCR22 | OCR21     | OCR20     | OCR19     | OCR18     | OCR17     | OCR16     |

| Вн             | FSR1 (RW)              | FSR7            | FSR6  | FSR5      | FSR4      | FSR3      | FSR2      | FSR1      | FSR0      |

| Сн             | FSR2 (RW)              | FSR15           | FSR14 | FSR13     | FSR12     | FSR11     | FSR10     | FSR9      | FSR8      |

| D <sub>H</sub> | FSR3 (RW)              | FSR23           | FSR22 | FSR21     | FSR20     | FSR19     | FSR18     | FSR17     | FSR16     |

| E <sub>H</sub> | CAPDAC_N (RW)          | -               | -     | CAPDAC_N5 | CAPDAC_N4 | CAPDAC_N3 | CAPDAC_N2 | CAPDAC_N1 | CAPDAC_N0 |

| F <sub>H</sub> | CAPDAC_P (RW)          | -               | -     | CAPDAC_P5 | CAPDAC_P4 | CAPDAC_P3 | CAPDAC_P2 | CAPDAC_P1 | CAPDAC_P0 |

R: Read only registers RW: Read/Write registers

Note: At reset all registers are initialized to  $00_{\rm H}$  on reset.

### CR1 (ADD: 03<sub>H</sub>) CONTROLREGISTER-1

| BIT7 | BIT6 | BIT5 | BIT4 | BIT3   | ВІТ2 | BIT1 | ВІТ0  |

|------|------|------|------|--------|------|------|-------|

| FS2  | FS1  | FS0  | OCEN | GCALEN | -    | EXC1 | EXC00 |

Bit 7-5 : FS2:FS1:FS0: Full Scale Input Capacitance  $C_{FS}$  Range Selection Bits.

Refer to Table 5 for more details

Bit 4: OCEN: Offset Calibration Enable bit

OCE = 1: Enable offset calibration OCE = 0: Disable offset calibration

Bit 3: GCALEN: Gain calibration Enable bit

GCALEN = 1: Enable Gain calibration GCALEN = 0: Disable Gain calibration

Bit 4: Not Used

Bit 1-0: EXC1:EXC0: Excitation Source Amplitude Selection Bits.

Refer to table 8 for more details

CR2 (ADD: 04<sub>H</sub>) CONTROL REGISTER- 2

| BIT7            | BIT6 | BIT5 | BIT4 | BIT3 | BIT2  | BIT1 | BIT0 |

|-----------------|------|------|------|------|-------|------|------|

| Data_<br>format | OLDD | ORDD | PRE1 | PRE0 | OSR10 | OSR9 | OSR8 |

Bit 7: Data\_format: Data format of the output code

Data\_format = 1: Uni-polar Output Data.

Data\_format = 0: 2's complement output data.

Bit 6: OLDD: Over-Load Detection Disable

OLDD = 0: Enable over-load detection.

OLDD = 1: Disable over-load detection.

**Bit 5: ORDD: Over-Range Detection Disable**

ORDD = 0: Enable over-range detection. ORDD = 1: Disable over-range detection.

Bit 4-3: PRE1:PRE0: Prescaler Bits.

Refer to Table 6 for more details.

Bit 2-0: OSR10: OSR9: OSR8: OSR control bits.

Three Most Significant Bits of 11 bits of decimation ratio.

## DECIM\_reg (ADD: 07<sub>H</sub>) Control Register - 3 (Read/Write)

| BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| OCR07 | OCR06 | OCR05 | OCR04 | OCR03 | OCR02 | OCR01 | OCR00 |

#### Bit 7-0: OSR7:OSR0

8 Least Significant Bits of 11 bit decimation ratio.

## FSR2 (ADD: 0C<sub>H</sub>) FULL SCAEE REGISTER-2

(Middle Byte)

| BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| FSR15 | FSR14 | FSR13 | FSR12 | FSR11 | FSR10 | FSR09 | FSR08 |

## OCR1 (ADD: 08<sub>H</sub>) OFFSET CALIBRATION REGISTER-1

(Least Significant Byte)

| BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| OCR07 | OCR06 | OCR05 | OCR04 | OCR03 | OCR02 | OCR01 | OCR00 |

## FSR3 (ADD: 0D<sub>H</sub>) FULL SCAEE REGISTER-3

(Most Significant Byte)

| BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| FSR23 | FSR22 | FSR21 | FSR20 | FSR19 | FSR18 | FSR17 | FSR16 |

# OCR2 (ADD: 09<sub>H</sub>) OFFSET CALIBRATION REGISTER-2

(Middle Byte)

| BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| OCR15 | OCR14 | OCR13 | OCR12 | OCR11 | OCR10 | OCR09 | OCR08 |

Note: 24-bit FSR (FSR3:FSR2:FSR1) holds the value in 2's Complement format. The value of FSR must always be positive.

## OCR3 (ADD: 0A<sub>H</sub>) OFFSET CALIBRATION REGISTER-3

(Most Significant Byte)

| BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| OCR23 | OCR22 | OCR21 | OCR20 | OCR19 | OCR18 | OCR17 | OCR16 |

Note: 24-bit OCR (OCR3:OCR2:OCR1) register holds the value in 2's Complement format. Its value can be positive and Negative.

### CAPDAC\_N (ADD: 0E<sub>H</sub>) (Read/Write)

| BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|------|------|------|------|------|------|------|------|

| DC23 | DC22 | DC21 | DC20 | DC19 | DC18 | DC17 | DC16 |

The CAPDAC\_N registers bits control the capacitance of CAPDAC\_N. The total capacitance of CAPDAC\_N is given as:

C<sub>CAPDAC\_N</sub> = 0.25 pF\*(Decimal Equivalent of CAPDAC\_N5:CAPDAC\_N0)

# FSR1 (ADD: 0BH) FULL SCAEE REGISTER-1

(Least Significant Byte)

| BIT7  | BIT6  | BIT5  | BIT4  | BIT3  | BIT2  | BIT1  | BIT0  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| FSR07 | FSR06 | FSR05 | FSR04 | FSR03 | FSR02 | FSR01 | FSR00 |

#### CAPDAC\_P (ADD: 0F<sub>H</sub>) (Read/Write)

| BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|------|------|------|------|------|------|------|------|

| DC23 | DC22 | DC21 | DC20 | DC19 | DC18 | DC17 | DC16 |

The CAPDAC\_N registers bits control the capacitance of CAPDAC\_N. The total capacitance of CAPDAC\_N is given as:

CCAPDAC\_N = 0.25 pF\*(Decimal Equivalent of CAPDAC\_N5:CAPDAC\_N0)

## DIGITAL\_CODE\_B3 (ADD: 00H) DIGITAL OUTPUT CODE

(MOST SIGNIFICANT BYTE)

| Bľ | T7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|----|----|------|------|------|------|------|------|------|

| DC | 23 | DC22 | DC21 | DC20 | DC19 | DC18 | DC17 | DC16 |

# DIGITAL\_CODE\_B2 (ADD: 01H) DIGITAL OUTPUT CODE

(MIDDLE BYTE)

| BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|------|------|------|------|------|------|------|------|

| DC15 | DC14 | DC13 | DC12 | DC11 | DC10 | DC09 | DC08 |

## DIGITAL\_CODE\_B1 (ADD: 02<sub>H</sub>) DIGITAL OUTPUT CODE

(LEAST SIGNIFICANT BYTE)

| BII7 | BI16 | BI15 | BI14 | BII3 | BII2 | BII1 | BIIO |

|------|------|------|------|------|------|------|------|

| DC07 | DC06 | DC05 | DC04 | DC03 | DC02 | DC01 | DC00 |

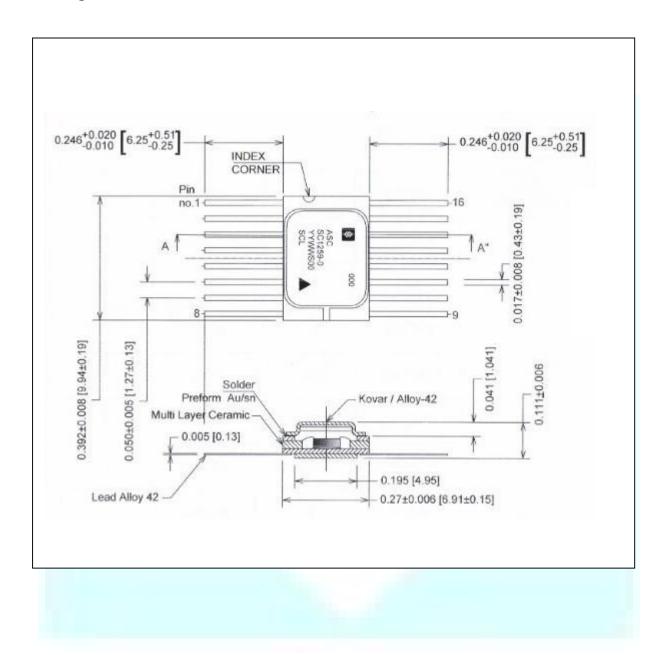

## **PACKAGE INFORMATION**

Package: 16 Pin CSOP

**NOTE:** All linear dimensions are in millimetres.

#### **TEST METHODS**

- 1. **Continuity test**: Ground all supply pins (AVDD, AVSS, DVDD and DVSS) of device. Force current 100μA to pin under test, Measure the voltage drop (Diode connected to AVDD/DVDD will be forward biased) and check it for pass/fail limit. Sink100μA current from pin under test, Measure the voltage drop (Diode connected to AVSS/DVSS will be forward biased) and check it for pass/fail limit.

- 2. Input gate leakage Low Test: Apply AVDD, DVDD equal to 3.3V. Preconditions all input pins to logic 0. Force individual input to AVSS/DVSS. Wait for 10ms and measure current. Fail if measured current (IIL) is less than -1μA.

- 3. Input gate leakage High Test: Apply AVDD, DVDD equal to 3.3V. Preconditions all input pins to logic 1. Force individual input to AVDD/DVDD. Wait for 10ms and measure current. Fail if measured current (IIH) is greater than +1μA.

- 4. Static IDD Current: Apply AVDD, DVDD equal to 3.3V. Preconditions all input pins to logic 0. Wait for 10ms. Measure current flowing into AVDD and DVDD pins. Fail if measured current is not within limits. Similarly measure current flowing into AVDD and DVDD pins with preconditioning all input pins to logic 1 and fail if measured current is not within limits.

- 5. On Temperature Sensor Test: Apply AVDD, DVDD equal to 3.3V. Wait for 50ms. Sink zero current (or <1µA) from REFOUT pin and measure REFOUT voltage. Fail if measured voltage is not within given limits. Similarly sink 2.5mA current from REFOUT and measure REFOUT voltage. Fail if it is not within limits. Calculate load regulation and check for pass/fail limit.

- 6. Register Integrity Test: Apply AVDD, DVDD equal to 3.3V. First write values 0x00/ 0xFF/ 0xAA/ 0x55 to all control registers (RW) then read all control registers and compare it with the written value. If read value does not match with written value mark the test as fail. Take care of failure before continuing next tests.

- 7. ADC Input Range Test: Apply AVDD, DVDD equal to 3.3V. Select Programming Mode. Apply reference supply 2.5V (REFP-REFN), clock 4MHz. Set PGA=1, OSR=2047 and f<sub>MOD</sub>=2MHz. Select input channel. Perform system offset and system gain calibration. Apply input -V<sub>REF</sub> to +V<sub>REF</sub> instep of 0.2\*V<sub>REF</sub>. Read ADC data output and check it for pass/fail limit. Calculate Non linearity using best fit line method and check for pass and fail limit. Repeat the test for all cores. Repeat ADC input range test for flight mode also.

- 8. **PGA Test:** Apply AVDD, DVDD equal to 3.3V. Apply reference supply, clock 4MHz. Set OSR=2047 and  $f_{\text{MOD}}$ =2MHz. Select input channel. Select PGA and perform system offset and system gain calibration. Apply input V<sub>REF</sub>/128. Read ADC data output for all PGA setting and for all core sand verify it for pass/fail limit.

- 9. Offset Error Test: Apply AVDD, DVDD equal to 3.3V. Apply reference supply 2.5V (REFP-REFN), clock 4MHz. Set OSR=2047 and  $f_{\text{MOD}}$ =2MHz. Select PGA equal to 1.

- Offset Error before Calibration: Apply 0V input. Read ADC data output and check for pass/fail limit.

- Offset Error after system offset calibration: Perform system offset calibration. Read ADC output and check for pass/fail limit.

Repeat for all PGA settings and for both the cores.

- 10. Full Scale Error Test: Apply AVDD, DVDD equal to 3.3V. Apply reference supply 2.5V (REFP-REFN), clock 4MHz. Set OSR=2047 and  $f_{\rm MOD}$ =2MHz. Select PGA equal to 1. Perform system offset calibration.

- Full Scale Error before Calibration: Apply V<sub>REF</sub>/PGA at input. Read ADC data output and check for pass/fail limit.

- Full Scale Error after system gain calibration: Apply V<sub>REF</sub>/PGA at input. Perform system gain calibration. Read ADC output and check for pass/fail limit.

Repeat for all PGA settings and for both the cores.

11. CMRR (Common Mode Rejection Ratio) Test: Apply AVDD, DVDD equal to 3.3V. Apply reference supply 2.5V (REFP-REFN), clock 4MHz. Set OSR=2047 and  $f_{\text{MOD}}$ =2MHz. Select input channel. Set PGA equal to 1. Short channel inputs INP and INN and apply input 0V, 1.65V and 3.3V with reference to AGND. Read ADC data output for 20 samples at each step and record average value. Calculate the CMRR as given below.

$$CMRR = -20 * (Log10 ((|ADCOUT_0 - ADCOUT_{VCM}|) / V_{CM}))) + (20 * (Log10 (PGA))$$

Where, ADCOUT<sub>0</sub> is average value of ADC output at 0V input and ADCOUT<sub>VCM</sub> is average value of ADC output at desired common mode input voltage. Check the calculated CMRR value for pass/fail limit. Repeat the procedure for all PGA settings and for both the cores.

12. ENOB (Effective number of Bits) Test: Apply AVDD, DVDD equal to 3.3V. Apply reference supply 2.5V (REFP-REFN), clock 4MHz. Set  $f_{\text{MOD}}$ =2MHz and OSR=2047. Select PGA equal to 1. Short channel inputs INP and INN and apply input 1.65V and read ADC output for 100 samples. Calculate ENOB as given below.

ENOB NOS =

$$24 - Log_2$$

(ADCOUT<sub>MAX</sub> - ADCOUT<sub>MIN</sub>) + 2.7

Where, *ADCOUT<sub>MAX</sub>* and *ADCOUT<sub>MIN</sub>* are maximum and minimum ADC output sample value. Check the calculated ENOB value for pass/fail limit. Repeat the procedure for all PGA settings and for both the cores.